求才詐騙

故事是這樣子的,前些日子遇到求才詐騙,雖然我不是很肯定他們要幹嘛,但總之機會難得(?就記錄一下好了

...故事是這樣子的,前些日子遇到求才詐騙,雖然我不是很肯定他們要幹嘛,但總之機會難得(?就記錄一下好了

...故事是這個樣子的,有一位強者我同學 JJL 大大,從大學到現在就一直罩我,本來他也有經營一個 hugo 的 blog 在 https://ys-hayashi.me/ (不用點了已經沒了),主要也是寫一些硬體和 FPGA 相關的內容。

...

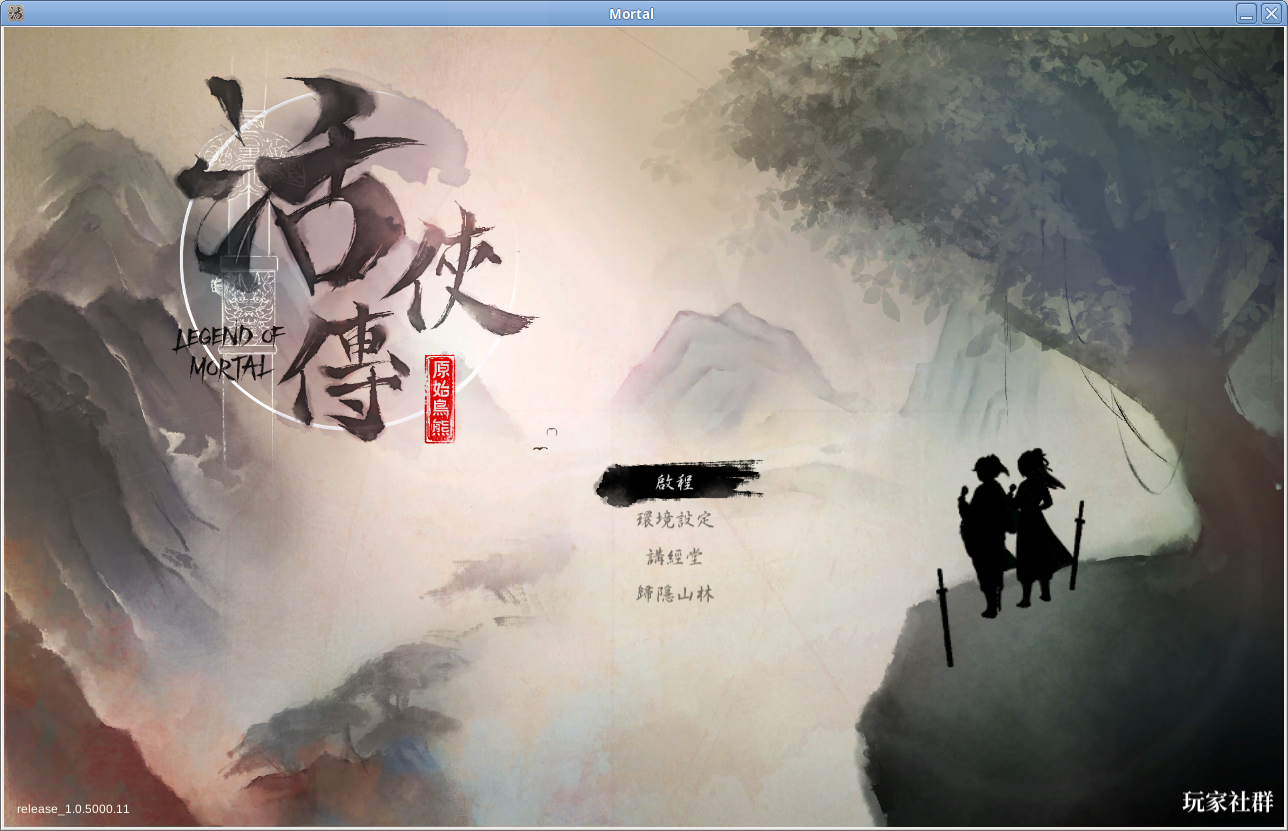

開頭先來一張第二輪結緣成功的雞腿俠鎮樓。

故事是這個樣子的,上一篇九日的評測

裡,提到順便一起買的有活俠傳,買了之後一直放著沒玩Steam 就是一個收集遊戲的遊戲。

當你身處戰國時代,周遊列國就是必要技能

在先前的 design contraint 與 design compiler 時都有提過,在晶片中會檢查每條 path - 也就是每組 register 間的 Delay 都能符合 Timing Constraint,這項檢查是重中之重,如果 Timing Constraint 達不到,晶片就只能降規格執行。

...這篇跟之前的 DFT 一樣,介紹一下 ECO 這個我還沒完全嘗試過的東西,我們在設計上要怎麼支援 ECO ,以及 Spare Cell 這個最常用在 Layout 上的 ECO 解決方案。

...故事是這樣的,最近小弟在公司接了一個專案,使用的製程只有 3 層金屬,跟之前使用過的如 .18 有 5 層金屬、90 nm 有 9 層、40 nm 有 10 層(嚴格來說也只有九層)相差甚遠,也因此造成一堆 innovus layout 上的問題, 值得寫篇文好好記錄一下。

...故事是這樣的,在龐大的硬體產業裡,沒有一家公司能獨立打造一顆晶片,即便是 Nvidia, AMD 這樣 Tier-1 的公司,也有許多的設計是來自授權的 IP(Intellectual Property)。

現代的晶片就像是堆 IP 積木一樣,每塊積木後面可能都是無數工程師的心血結晶,以及耗費鉅資驗證與最佳化的結果。

故事是這樣子的,最近讀了一些商業相關的書,發現在經營上應該更有策略一些,加上觀察到強者我同學 ShingLyu 的 blog

在單月瀏覽人次上整整比小弟多了 8 dB 左右,顯見英文內容和中文內容的引流能力還是天差地遠。

有了這樣的結論,提供英文內容似乎就是大草原不可避的了,那麼要怎麼把我的 blog 快速轉成英文內容呢?

| 書名 | 供應鏈戰爭:砂、鹽、鐵、銅、鋰、石油的戰略價值 |

| 原書名 | Material World: A Substantial Story of Our Past and Future |

| 作者 | Ed Conway |

| 譯者 | 譚天 |

| 出版商 | 天下文化 |

| 出版日 | 2023-11-30 |

| ISBN | 9786263555136 |

首先我必須說,台灣書商都會下一些比較聳動的標題,就像這本供應鏈戰爭跟副標的戰略價值。

事實上你看原文 Material World: A Substantial Story of Our Past and Future,

其實指的是內文作者發明的用詞 原料世界或者是物質世界,副標也只是人類的過去與未來的故事,壓根沒想到戰爭與戰略。

在現代晶片設計中,隨著晶片功能越來越複雜、邏輯閘數量動輒上億,如何確保晶片在製造後能夠正確運作,成為一項極具挑戰性的課題。

經過 design compiler、INNOVUS 等 EDA 軟體的努力,設計的時序本身沒有錯誤,製程的變異也可能導致晶片出現缺陷。

因此,我們需要一套有效的方法,在晶片出廠前對內部進行全面測試,這就是 DFT(Design for Testability) 出場的時機了。