讓 Verilator 倒波形快還要更快

Verilator 是目前開源乃至於硬體免費仔(欸)的第一首選,雖然它在使用方式上相對複雜, 但你想它身為開源工具,完整支援 systemverilog ,還能有這麼快的模擬速度,到底還有什麼好嫌的呢?

...IEEE1735 簡介

在上篇講 Silicon IP 的文 我們稍微提到過 IEEE1735 ,不過後來我發現 IEEE1735 的原理可以講得更深入一些,主要是多解釋一些 IEEE1735 會對 HDL 檔案造成的影響。

...數位電路設計系列 - 數位電路設計系列 - Signoff

故事是這樣子的,無論是數位、類比還是微波電路,在晶片的最後一步,都要進行所謂的 signoff 流程,進行最終的檢查看看設計有沒有問題等等。

...從指定 commit 生成全新的 git 倉儲

故事是這樣子的,最近用了 git filter-branch 把手邊一個 repository

整理了一遍,因為中途一度碰觸到搜尋引擎也很難搜到的東西AI 的邊界,

所以就來記錄一下。

求才詐騙

故事是這樣子的,前些日子遇到求才詐騙,雖然我不是很肯定他們要幹嘛,但總之機會難得(?就記錄一下好了

...超爽的,撿到一堆文勒

故事是這個樣子的,有一位強者我同學 JJL 大大,從大學到現在就一直罩我,本來他也有經營一個 hugo 的 blog 在 https://ys-hayashi.me/ (不用點了已經沒了),主要也是寫一些硬體和 FPGA 相關的內容。

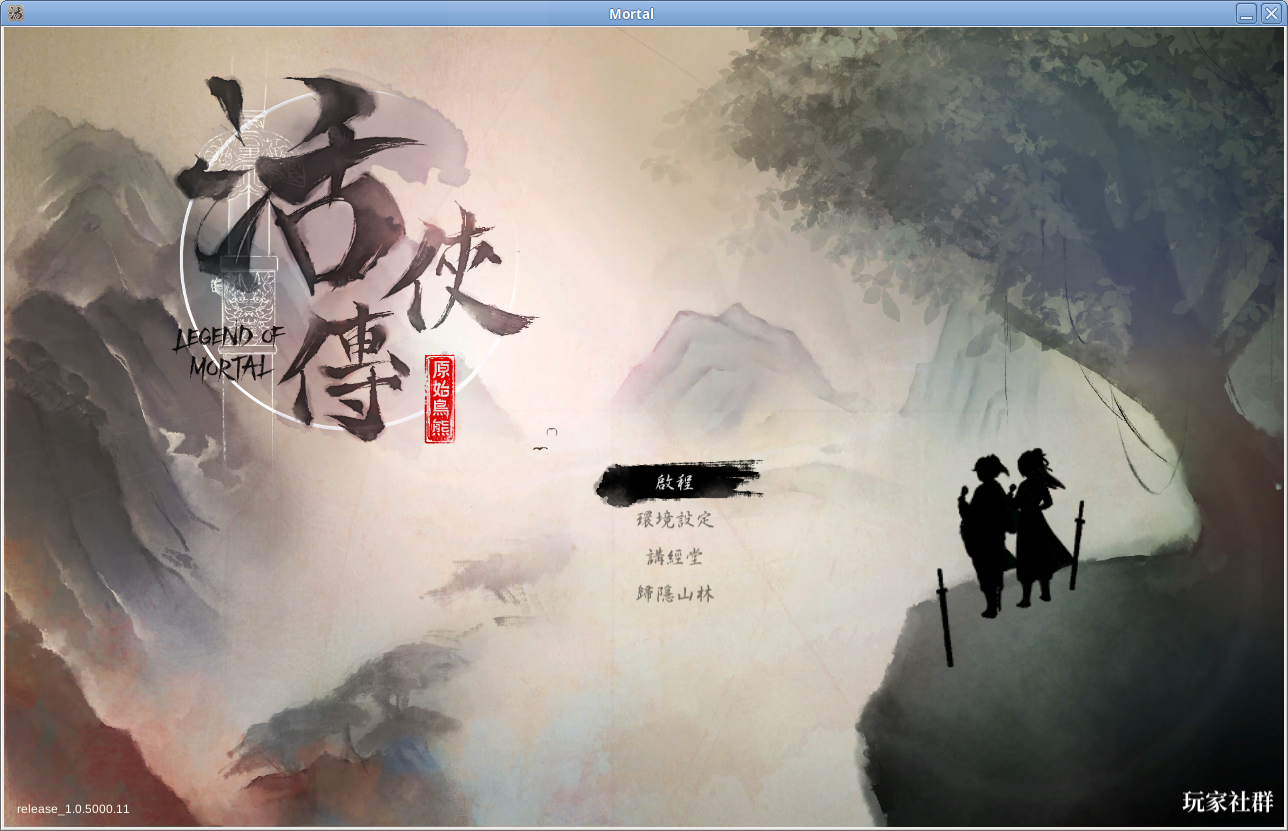

...遊戲心得:活俠傳

開頭先來一張第二輪結緣成功的雞腿俠鎮樓。

故事是這個樣子的,上一篇九日的評測

裡,提到順便一起買的有活俠傳,買了之後一直放著沒玩Steam 就是一個收集遊戲的遊戲。

RC Extraction 設定

當你身處戰國時代,周遊列國就是必要技能

在先前的 design contraint 與 design compiler 時都有提過,在晶片中會檢查每條 path - 也就是每組 register 間的 Delay 都能符合 Timing Constraint,這項檢查是重中之重,如果 Timing Constraint 達不到,晶片就只能降規格執行。

...ECO cell 與 Spare Cell

這篇跟之前的 DFT 一樣,介紹一下 ECO 這個我還沒完全嘗試過的東西,我們在設計上要怎麼支援 ECO ,以及 Spare Cell 這個最常用在 Layout 上的 ECO 解決方案。

...1P3M 下要怎麼 layout

故事是這樣的,最近小弟在公司接了一個專案,使用的製程只有 3 層金屬,跟之前使用過的如 .18 有 5 層金屬、90 nm 有 9 層、40 nm 有 10 層(嚴格來說也只有九層)相差甚遠,也因此造成一堆 innovus layout 上的問題, 值得寫篇文好好記錄一下。

...