c++ static 修飾詞

最近寫基因演算法的project,有需要使用到C++ class的static variable,因為我之前這個東西怎麼寫都會出錯, 這次好不容易在強者陳仕勳(GodGodMouse)的指導下成功寫出可以用的static,在這裡記錄一下怎麼使用C++的static(是說這些文章也多到滿出來了)。

...最近寫基因演算法的project,有需要使用到C++ class的static variable,因為我之前這個東西怎麼寫都會出錯, 這次好不容易在強者陳仕勳(GodGodMouse)的指導下成功寫出可以用的static,在這裡記錄一下怎麼使用C++的static(是說這些文章也多到滿出來了)。

...這幾天在讀電磁學,發現一個自己沒想過,卻滿基本的問題:

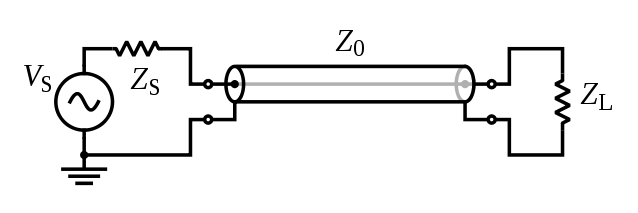

我們先拿一個最芭樂的傳輸線模型,如下所示:

現在假設 Vg=1V,Zs = 50Ω,Z0=50Ω,ZL=25Ω,線長λ/4(懶…選個簡單一點的數字) 請問從傳輸線入射的功率為?

解法一:在Zs和傳輸線的交點分壓 P = ½ * ( 1 * 50/(50+50) )^2 / 50 = 2.5mW

解法二: 25Ω經過傳輸線得到Zin = 100Ω,與Zs=50Ω分壓去解,得到2.222mW

為什麼兩個答案是不一樣的?

...其實這是整理在BBS上的舊文,想說就把它轉到這裡來,是記錄如何在程式裡面加上顏色的控制,如果熟BBS的人應該很熟悉, 似乎是一個公訂的標準上色方式,大家參考參考,也許可以讓你的程式增添不少色彩,能不能為人生上色就說不準了。

...最近梗比較少,寫不出什麼有用的東西

整理了一下自己的vim設定,就把自己的設定跟plugin分享一下好了

最近因為筆電快要解體,不開玩笑,像正面偵測螢幕的按鈕竟然掉下來了。

就趁著八月台北資訊展時入手一台,因為平常要跑很多模擬的程式,需要的是運算力強的機種,本人又是個效能控XD, 也不想盯著太小的螢幕,經過綜合評估,最後入手的是這台 ACER Aspire V3-571G,近日解禁,於是來寫個不正經的開箱文:

...正規表示式是個強大的工具,定義了明確的定串比對規則,來幫助使用者把梳字串,在很多程式都有支援,如 Linux shell 的grep, awk, sed,vim的搜尋取代功能等, C語言的scanf其實也有支援,可惜正規表示法規則甚多,一時之間難以記全。

這篇主要記錄正規表示法的規則,整理自"Practical Programming in Tcl and Tk"第十一章,給自己做個參考:

...很有趣的,在大學最後兩年的暑假,分別參加了YEF和Tic100兩個國內大型的創業競賽,雖然說結果都不是很好,YEF最後沒選上代表,tic100進了決賽之後就被刷掉了,不過,在參加完之後,對這類創業競賽也有一些自己的想法和心得,在這裡分享給大家。

...testbench是verilog另一個很好用的功能,一般來說,如果設計的電路是要完成某個特定的演算法,比如我們在實驗中要實作256bits的montgomery algorithm,把電路透過quartus合成、燒進FPGA執行,透過Logic analyser分析行為實在太曠日費時(那時寫的不好,合成一次就要30分鐘= =)。

這時候testbench出現了,testbench提供了一個方式,讓我們能利用軟體模擬電路的行為,看看電路的反應,每次模擬只需要幾秒鐘,就可以得到電路的行為。

在上一篇裡面,我們談過了verilog 三大塊的寫法,以及常見的verilog錯誤,那現在就來看看,一個verilog module的構成,

其實一個module,就好像在寫一個完整的電路,有哪些input, output,要有多少個register,之間的接線,甚至要包住其他的module,是一塊很完整的block。

感謝鄭為中大神的提醒,要寫這篇verilog常見錯誤文,也感謝鄭為中大神對我 verilog 觀念的澄清:)

譔寫verilog最常見的錯誤,當然就是syntax error……= =

當然這裡不討論這些,雖然他們很常出現,像忘了加分號、拼錯字之類的,我們延續上一篇對verilog結構的討論,再來看看,寫得不好的verilog code會造成怎麼樣硬體上的後果,與上一篇結構問題相同,需要轉成硬體的結果造成這個verilog獨有的錯誤。